# **EXAMPLE ARCHITECTURE**

April 2017: Computing Systems Week, Zagreb

Advancing the digital healthcare revolution

A quantum computing breakthrough

**HiPEAC Technology Transfer Award winners**

#### contents

37 nations represented at HiPEAC17

Bringing the computing revolution to healthcare for a changing population

**Innovation Europe**

- 3 Welcome Koen De Bosschere

- 4 Policy corner An update on European policy on digital technologies Sandro D'Elia

- 5 News A round-up of the latest news from our community

- 10 Healthcare special Bringing the computing revolution to healthcare for a changing population IT4Innovations, AEGLE project, TU Delft, Nanostream project, TULIPP project

- 16 Innovation Europe HARPA: Cost-efficient ways to manage performance variability Dimitrios Soudris

- 17 Innovation Europe The MIKELANGELO Approach to HPC Simulations and Aircraft Design Marta Stimec

- 18 Innovation Europe ASAP: flexible & scalable data analytics Polyvios Pratikakis

- 19 Innovation Europe Making mobile devices more secure with the ASPIRE Framework Bjorn De Sutter

- 21 Innovation Europe Leading data centres into the future: EUROSERVER John Thomson

- 24 Tech Transfer Award winners 2016 HiPEAC Technology Transfer Awards

- 26 Industry focus A runtime parallelization approach for shared memory architectures Luigi Pomante

- 27 EU project to spin-off ParaFormance™: Democratizing Multi-Core Software Chris Brown

- 29 Peac performance QuTech and Intel demonstrate full stack implementation of programmable quantum computer prototype Nader Khammassi

- 32 Peac performance Leopard: a high-performance processor for critical real-time software Jaume Abella

- 34 Peac performance Technology opinion: FPGA acceleration goes mainstream Magnus Peterson

- 35 HiPEAC futures

Career talk: Darko Gvozdanović, Ericsson Nikola Tesla HiPEAC collaboration grants: Amit Kulkarni HiPEAC internships: Amardeep Mehta Three-minute thesis: Foivos Zakkak Postdoc funding focus: ERC Starting Grants: David Black-Schaffer

2016 HiPEAC Technology Transfer Awards

Technology opinion: FPGA acceleration goes mainstream

**HiPEAC futures**

HiPEAC is the European network on high performance and embedded architecture and compilation.

HiPEAC has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement no. 687698.

Design: www.magelaan.be Editor: Catherine Roderick, Madeleine Gray Email: communication@hipeac.net The internet is disrupting everything... and fast. As more and more information, both recent and historical, becomes available, and as search engines become more powerful in interpreting unstructured information on the internet, our privacy is being invaded in unprecedented ways. Even if you do not disclose any information about yourself on social media, this will not stop others from sharing information about you. Denying that you know somebody is pointless if you appear in the background of a selfie taken by a tourist while talking to that person. High resolution pictures can reveal information that is not visible to the naked eye like messages on a smartwatch or a smartphone, or notes jotted down on a piece of paper. Even confidential documents get disclosed on WikiLeaks. Cover-up operations are often failing because it is very difficult to delete digital evidence on the internet.

The consequence is that candidates who run for highly competitive elective offices become very vulnerable. With millions of eyes zooming in on all available information, there are always things that can be used by an opponent to damage a candidate. On social media, anybody can create a storm based on real or fake news. Messages are copied, liked or retweeted at the speed of light. By the time facts have been checked and analysed, the damage to a reputation has long since been made. There are no places to hide from such a storm on the internet. Recently, there seems to have sprung up a new generation of politicians who have developed a strategy to deal with this situation. Instead of defending themselves, they just ignore the news, calling it a conspiracy, not relevant or fake, and continue their business as usual. The internet is known to cause disruption in many sectors. Could this be sign of the beginning of disruption in politics, a disruption that might make the political profession harsher and in which only the toughest men and women can survive and thrive? If this were to be the case, it is definitely not the disruption I was hoping for.

The theme of this HiPEAC magazine is health. Health is the second biggest market for embedded systems in Europe (after automotive and before military and aerospace). This means that developing IT-solutions for challenges in healthcare is a very good opportunity to generate impact. I wish you pleasant reading and I hope that the research and innovations presented in this magazine will inspire you.

Koen De Bosschere, HiPEAC coordinator

#### **Policy corner**

# An update on European po

Sandro D'Elia of the Technologies and Systems for Digitising Industry unit at the European Commission updates us on progress in the various EU digital initiatives.

Most of the work of my office in the European Commission is centred on 'Digitising European Industry', the initiative aiming to 'ensure that any industry in Europe, big or small, wherever situated and in any sector can fully benefit from digital innovations to upgrade its products, improve its processes and adapt its business models to the digital change'. This started in 2015, and it's time to look back at what we have learned.

The most important feedback that we have got in the last few months is the enormous interest in the initiative across Europe. There are lots of meetings, events and workshops on this subject, across all industry sectors from manufacturing to health, transport or energy, and the message we get is invariably the same: this is something being taken very seriously and that is greatly needed for the future of Europe. Everybody is aware that there is no other option: European industry has to embrace digital technologies to stay innovative, and has to stay innovative to survive.

"EU-level cooperation is needed to achieve results"

A second message that we get is the widespread awareness of the possible negative impact of digitization on employment. We know that many jobs have already been replaced by computers, and that even more jobs will be replaced in the future by cyber-physical systems with varying degrees of autonomy, or by artificial intelligence. To create the new jobs that will replace the lost jobs, Europe needs digital skills across all sectors: not only programmers but also people capable of interacting with robots, training neural networks and generally using the technology of tomorrow in any aspect of life and work. This requires collaboration between the education system and industry; the HiPEAC community, which has one foot in the world of industry and the other in academia, can play a significant role.

The third message is the need for collaboration. The country most advanced in the digitization of industry is probably Germany, which invented the concept of 'Industrie 4.0', but even its government clearly says that this cannot be a national effort. EU-level cooperation is needed to achieve results, and the network of 'Digital Innovation Hubs' that we are trying to build will play an important role in spreading digital technology across all regions.

Of course, this requires adequate investment. The European Commission contributes directly through the Horizon 2020 programme, which dedicates several challenges to the digitization of industry. For example I4MS (Innovation for Manufacturing SMEs) aims to create innovation hubs and transfer technology to SMEs across Europe; other challenges aim to fund the development of digital industrial platforms.

It should be clear that the funding available from H2020 is too limited to achieve impact across all of Europe, and should be considered only as 'seed money': it will be useful to kick-start new initiatives and to guarantee coordination between local initiatives across Europe – in other words, to foster the European dimension which is needed to reach critical mass. However, Digital Innovation Hubs need long-term and stable funding, which is not

#### Policy corner

# licy on digital technologies

compatible with H2020 rules, so they will have to get their main financial support from other sources: local governments, national programmes, or European Regional Development Funds.

In this context, there is no 'one size fits all' solution: every innovation hub will have to find their best way to support its local industry. The European Commission will only have the role of supporting coordination and collaboration across Europe, namely through the Platform of National Initiatives which was launched at the end of March in Rome. In the same week another important event took place, which is also very relevant for the HiPEAC community: the launch of the European High-Performance Computing initiative, in which several Member States join forces to develop the next generation of 'exascale' computers, designed and built in Europe.

So, many things are shaping the digital policy of Europe in the coming months, and all these initiatives fall under the big umbrella of DSM, the 'Digital Single Market'. DSM has already delivered some spectacular results such as the reduction of data roaming costs across Europe. However, even more important are the ongoing activities in the areas of regulation for data ownership, free flow of data, liability and security, and autonomous systems. All these areas are prerequisites for our work in digital technologies: legal certainty is needed for investments in, e.g. big data or autonomous robots, and rules have to be coherent across Europe. If this does not happen, competitors in the US and China will outperform European industry thanks to the advantage they

have in their home markets, which are true digital single markets.

This issue of the HiPEAC magazine has a special focus on healthcare, which is a very clear example of the need for a DSM in Europe: just think how data ownership and data privacy are important for the health profession. Who should own the data from your fitness sensors? Should the doctor that you see while on holiday be able to access your medical data from another hospital? Will you have the right to be informed in real time if your elderly grandmother becomes ill? Should you be free to bring your health insurance data with you when you move to another country? All these questions are very practical, but do not have a consistent solution across Europe. A DSM is needed to guarantee high quality of services and, of course, to also make the European healthcare sector efficient.

To summarize: what is happening now in the field of European policy will have a strong impact on the future development of digital technologies in all application areas. As a professional in the field, I advise you to stay tuned and to follow future developments closely, as they will be relevant not only for the overall market, but very likely also for your future career choices.

## Welcome to Computing Systems Week Spring 2017 from Mario Kovač

HiPEAC: Mario, you were involved in the development of MP3 players and have a patent for JPEG compression. What new multimedia technologies are you excited about?

**MK**: There are several. For example, with IP video traffic reaching almost 90% of global consumer traffic by 2018 (as presented in the recent market analysis by Cisco), and given the plethora of devices on the market, the need to efficiently process and deliver video content will require enormous (exascale and beyond) HPC processing capabilities. Novel architectures and programming paradigms will need to be used to tackle this problem, but the results will enable companies in various market segments (including entertainment, health and security) to pro-

vide attractive and efficient new products and services. Our current research is strongly focused on this HPC/cloud architecture and application domain.

# HiPEAC: You're also part of the EU's Expert Horizon2020 Leadership in Enabling & Industrial Technologies ICT Committee. What do you think Europe should be focusing on in terms of industrial ICT?

**MK**: An interesting new H2020 LEIT ICT work programme is currently in the definition process and hereby I encourage all of the HiPEAC community to participate in this process. We all know that ICT is both driver and enabler of industrial growth, so investments in technological development of ICT industry and integration of ICT in all segments of our industry is an important factor. Also, Europe has been dependent on non-EU processor technology for years. There are new EU initiatives that will try to change this, which I strongly support.

### HiPEAC: What's the technology scene like in Zagreb? Also, where's the best place to grab a beer after a long day at CSW?

**MK**: Croatia is small country but the technology scene here is healthy and vibrant. The combination of good education and the possibility to provide ICT solutions/ services globally makes this industry segment prosperous and competitive. As for a place to relax, with the centre of Zagreb being close to the CSW venue there are a number of places to have coffee, dinner and a few beers later. Some most popular spots in the centre are around Cvjetni trg (Flower Square) / Bogovićeva Street or Tkalčićeva Street.

#### Some useful Croatian for your time at CSW

Hi, I'm John and I'm great at computer science.

Bok, ja sam John i rasturam računarstvo.

I am lost. Please show me the way back to CSW.

Oprosti, izgubio sam se. Kako da se vratim na CSW?

Where's the nearest bar?

Gdje je najbliži kafić?

## New impetus for Czech researchers in computing systems

Continuing the series of workshops in EU new member state countries, HiPEAC led a workshop at IT4Innovations in Ostrava, Czech Republic on 21 February. The aim of the workshops, which have been running since 2012, is to communicate to researchers in EU 'new member states' what HiPEAC is and what it does.

Representatives of five different technical universities as well as several companies came together in Ostrava for a very beneficial workshop hosted by IT4Innovations, the national supercomputing centre of the Czech Republic. Koen De Bosschere and Rainer Leupers presented the benefits of membership of the network for researchers from both academia and industry. Their presentations were followed by introductory talks by the attendees, which outlined the computing systems research ecosystem in the Czech Republic. Three blocks of presentations took place. The first was dedicated to speech and video processing. The second showcased Czech research related to low-power, high-performance computing. The final section was composed of talks on embedded systems and processors, networks and FPGAs. Prof. De Bosschere summarized his overall impression from the presented topics saying that: 'Had the presentations been anonymous, it would have been very difficult to tell whether they came from the Czech Republic, or from one of the "old member states". The research presented was of excellent quality. Several research outcomes were the result of European research projects, which shows that colleagues from the Czech Republic successfully compete for international research funding. HiPEAC membership can further expand their network, and get them involved in even more project proposals.

The HiPEAC network hopes to welcome more members from the Czech Republic as result of the workshop.

# **37 nations represented at HiPEAC17**

550 people from 37 countries came to a very sunny Stockholm 23-25 January for the annual HiPEAC conference. Over the years, it has developed into Europe's premier forum for experts in embedded and high performance systems architecture and compilation to network, forge new partnerships and find out about the latest developments in the field.

One of the reasons for the conference's popularity is the varied nature of the technical programme which is supported by exhibitions of university, project and industry-led research and innovation, and talks from companies. This year's company speakers came from both global giants like Intel and Ericsson and European SMEs including Silexica, Synective and INSYS. Keynote talks by Kathryn McKinley (Microsoft Research), Sarita Adve (University of Illinois at Urbana-Champaign) and Sandro Gaycken (ESMT Berlin) discussed data centre tail latency, memory coherence and consistency, and the immensity of the cybersecurity challenge.

The conference saw the launch of two startups: ZeroPoint Technologies (Gothenburg), which is in part a spinoff of the EC-funded EUROSERVER consortium, and Matryx Computers, the new business line of Embedded Computing Specialists. ZeroPoint is developing innovative compression technology with the potential to significantly compress the content of the cache and memory system while Matryx Computers specializes in FPGAbased embedded computers and operating systems for connected devices.

The Swedish capital, birthplace of Skype and Spotify and home to a vibrant tech startup scene, made an excellent host city, with the conference dinner taking place at the spectacular Stockholm City Hall. General Chairs Mats Brorsson and Zhonghai Lu of KTH Royal Institute of Technology in Stockholm noted the all-round positive ambience: 'We received a lot of positive feedback about the programme and the venue at the Waterfront Congress Centre. Three excellent keynote speeches led what has been a very interesting and diverse schedule of activities,' commented Mats Brorsson. 'It's been a very enjoyable experience to chair this edition of the HiPEAC conference and having been able to count upon the support of a very experienced conference committee! I'm now looking forward to attending HiPEAC 2018,' added Zhonghai Lu.

Werner Steinghögl of the EC's DG Communications Networks, Content & Technology, addressed a plenary session audience on the Digitising European Industry initiative, which aims to support and link up national initiatives for the digitization of industry and related services across all sectors and to boost investment through strategic partnerships and networks.

On the final day, Workshops and Tutorials co-Chair Diana Göhringer of Ruhr-University Bochum was awarded a HiPEAC Distinguished Service Award for her efforts in running this core element of the conference over the past three years.

The HiPEAC team would like to thank the conference sponsors, without whose generous support the event could not have been such a success.

See the keynotes speeches and other highlights at www.hipeac.net/youtube

Photo: Bagus Wibowo

## Design for reliability in the era of the computing continuum

Concluded in Autumn 2016, the EU-funded CLERECO (Cross Layer Early Reliability Evaluation for the Computing cOntinuum) project proposed a scalable, cross-layer methodology and supporting suite of tools for accurate and fast estimations of computing systems' reliability.

As we enter the era of nanoscale devices, reliability is becoming a key challenge for the semiconductor industry. The now atomic dimensions of transistors result in a vulnerability to variations in the manufacturing process and can dramatically increase the effect of environmental stress on the correct circuit behaviour. Failures in early assessing computing systems' reliability may produce excessive redesign costs, which can have severe consequences for the success of a product.

Current practice involves a worst-case design approach with large guard bands. Unfortunately, application of this approach is reaching its limit in terms of economic sustainability with regard to performance, size and energy costs. Coordinated by Dr Stefano Di Carlo of the Polytechnic of Turin, the CLERECO project aimed to address this challenge by focusing on reliability analysis in the early phases of the design. Early assessment within the design cycle provides the freedom for adaptive modification if the estimated reliability level does not meet the requirements. CLERECO methodology provides dedicated tools to separately analyse the technology, the hardware components (at the microarchitecture level) and the software modules of a complex system and to recombine the characteristics of single objects into a complex statistical Bayesian model. This can be used to perform statistical reasoning on the reliability of the system as a whole.

See the full version of this story at bit.ly/2mLHwn6

### HiPEAC members win prestigious CGO Test of Time award

A big round of applause to HiPEAC members John Cavazos, Grigori Fursin, Mike O'Boyle, Olivier Temam, and their co-authors Felix Agakov and Edwin Bonilla for winning the Test of Time award for their CGO'07 research paper on 'rapidly selecting good compiler optimizations using performance counters' (dl.acm.org/ citation.cfm?id=1252540). This annual award recognizes outstanding papers published at the

International Symposium on Code Generation and Optimization (CGO) one decade earlier, whose influence is still strong today.

This paper set an early example of the benefits of applying machine learning to compiler optimization. Importantly, it also led to realizing the challenges of transferring this research into production: the need to perform and process a huge number of rigorously controlled experiments to train predictive models, all in the presence of the continuously evolving software and hardware stack.

These challenges motivated Dr. Grigori Fursin to continue this research as a community effort. He created an open-source framework to share research artifacts (workloads, data sets, tools, models, features, scripts) as reusable components with JSON API, crowdsource experimentation across diverse hardware and inputs provided by volunteers, continuously learn most effective optimizations, collaboratively discover important SW/HW features to improve predictive models via a public repository of knowledge at cKnowledge.org.

Ten years on, this collaborative approach to performance optimization is used and extended by dividiti, ARM, General Motors, IBM, Imperial College, University of Edinburgh, University of Cambridge and other leading universities and companies to develop faster, cheaper, more power-efficient, and more reliable computer systems. It also helped initiate the Artifact Evaluation initiative at the CGO, PPoPP, PACT and other premier conferences to encourage artifact sharing and reuse, as well as independent validation of experimental results: cTuning.org/ae.

Dr Fursin commented: 'We would like to thank the community for strong interest in our machine learning and community based optimization techniques over the past ten years. We also encourage you to join our community effort to accelerate computer systems research and thus enable efficient, reliable and cheap computing everywhere - from IoT devices to supercomputers!'

## Award for TUDelft Team in International Big Data Apache Spark Competition: Ultra Fast and Low Cost Personalized DNA Analysis Using Big Data Approach

A team from the Computer Engineering Lab at Delft University of Technology team won the \$25,000 2nd prize in the Big Data Apache Spark hackathon competition held in New York City.

This is an international competition in which contestants compete to create an innovative big data solution that addresses relevant societal challenges using publicly available datasets and big data techniques. The competition generated much interest, attracting more than 500 registered contestants, with 23 teams making it to the finals. The TUDelft team created a platform called DoctorSpark to enable high performance and low-cost computation of DNA analysis programs using the Apache Spark big data framework. This platform enables faster DNA diagnostics in hospitals and clinics for patients suffering from cancer or other genetic disease. The results were announced

during the Data First Event in New York on 27 September 2016. More information about the winning project can be found at http://devpost. com/software/scalable-dna-analysis-pipelines-using-sparkz

#### **Cristina Silvano named 2017 IEEE Fellow**

Professor Cristina Silvano of the Politecnico di Milano has been named an IEEE Fellow 'for contributions to energy-efficient computer architectures'. The IEEE grade of Fellow is conferred by the IEEE Board of Directors upon a person with an outstanding record of accomplishments in any of the IEEE fields of interest. The

total number selected in any one year cannot exceed one-tenth of one percent of the total voting membership. IEEE Fellow is the highest grade of membership and is recognized by the technical community as a prestigious honour and an important career achievement.

At the early stages of her career, Cristina was part of the Bull-IBM Research team for the design of a family of scalable multiprocessor systems based on the PowerPC architecture, introduced in 1992 by Apple-IBM-Motorola. She then started investigating power optimization and estimation techniques for embedded architectures applied to the Lx/ST200 VLIW processors, designed in partnership between HP Labs and STMicroelectronics and widely used in a variety of embedded media processing products.

Her research interests are in the design of energy-efficient computer architectures with special emphasis on design space exploration and application autotuning for embedded manycore architectures. In these areas, she has coordinated several funded projects, including two EU-funded projects (MULTICUBE and 2PARMA). She is also active in the area of autotuning and adaptivity for energy-efficient HPC systems. On this topic, she is currently the Scientific Coordinator of the H2020 FET-HPC ANTAREX research project.

Prof. Silvano is an active member of the scientific community and served as General Chair and Program Chair of several conferences and workshops on computer architectures and design automation. She is Associate Editor of the ACM Transactions on Architecture and Code Optimization and served as independent expert reviewer for the European Commission and for several science foundations.

She has over 160 publications in peer-reviewed international journals and conferences, four books and has made several industrial patent applications. Europe's national healthcare systems face huge challenges, including an aging population and the inevitable burden of chronic diseases and conditions, and limitations on economic resources. These have placed new demands on healthcare systems and so, to remain sustainable and meet populations' needs, a shift is required in the way that services are managed, delivered and funded.

# Bringing the computing revolution to healthcare for a changing population

In terms of information and communication technology, a big data approach is needed to help address problems faced by traditional healthcare applications. As this article shows, these have access to a limited set of data, which is usually fragmented and stored in different and hard-to-access sites. As such, the introduction of increased automation into the healthcare sector has never been more appropriate.

Digital healthcare systems can offer a number of benefits, such as improved connectivity, information integration and data capture, increased of analytic and diagnostic speed and accuracy and long-term cost savings. They can also facilitate patient empowerment, enabling them to play a more active role in the management of their own health, and receive personalized medicines and health plans.

Reliance on such techniques is increasing, which means that the potential for growth in the digital health sector is huge.

However, the shift towards digital healthcare brings its own unique challenges, as reliability and security of the information captured by digital systems and devices is paramount. This has meant that development and evolution within the medical IoT sector has been slower than other digitized fields, due to the high levels of regulation and validation needed to bring products to market. Add to this the significant technical tasks of dealing with massive amounts of data, or the rigorous performance required by medical applications within minimal power or space constraints, and it is easy to see the complexity of bringing new health technologies to market.

In this special feature, we explore a few examples of how the HiPEAC community is at the heart of this revolution, developing cutting-edge biomedical technologies and enhancing the capacities and capabilities of existing ones. Whether it is helping to model the human brain, building a European ecosystem for large scale clinical data management, harnessing the power of highperformance systems for medical imaging, or adapting financial applications to intensive care, HiPEACers are laying the foundations for the healthcare of tomorrow, by trying to meet the demands of today.

You can read more on this topic in the 'Career talk' on page 35 with Darko Gvozdanović of Ericsson Nikola Tesla, which is leading the way in European eHealth systems.

#### HIGH PERFORMANCE COMPUTING IN MEDICAL IMAGING

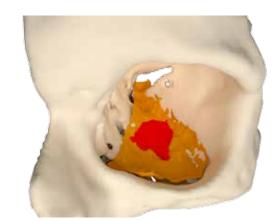

Researchers at IT4Innovations in the Czech Republic are constantly searching for new research directions and areas where high-performance computing (HPC) technology can be put to good use. One of our most important collaborations is with medical doctors from the University Hospital in Ostrava, Czech Republic, working on methodology for more precise measurement of orbital (eye socket) fracture size.

Very specific and precise information is required to assess the seriousness of orbital floor fractures – fractures at the base of the eye socket. Such assessments in turn determine whether patients should undergo surgery or whether less invasive treatment should be given instead. Computed Tomography (CT) or Magnetic Resonance Imaging (MRI) scanners are currently used by doctors to create three-dimensional virtual models from two-dimensional CT and MRI images. The extent of an orbital floor fracture is determined directly from CT images using a simplified empirical approach.

"We have developed parallel versions of all the tools for image processing, dramatically reducing analysis time and ensuring that patients receive the correct treatment sooner"

Although the use of CT and MRI technology raises standards in diagnostic medicine, the process generates large amounts of data. It is not only very time-consuming and labour-intensive to analyse this data, but also inefficient because not all the required information can be extracted from such virtual models. Utilizing resources available at IT4Innovations, we have developed parallel versions of all the tools for image processing outlined below, dramatically reducing analysis time and therefore ensuring that patients receive the correct treatment sooner.

3D virtual model of eye socket (white), orbital floor (orange) and fracture (red)

To construct three-dimensional models from two-dimensional data sources, we start by using filters such as Gaussian smoothing, anisotropic diffusion or BM3D to reduce noise in the CT images. Secondly, k-means clustering is used for image segmentation. In this step, the image is simplified to allow us to localize objects and their boundaries. Finally, we use the Poisson method for surface reconstruction. After analysis of the 3D models, doctors carry out validation exercises, which helps us to improve existing algorithms, thus enhancing the accuracy of measurements of orbital floor fractures.

Overall, we expect this collaboration to lead to virtual models of the orbital floor with minimal user intervention, which would allow doctors to more precisely establish the size of orbital floor fractures and therefore make better decisions about the treatment of patients.

#### www.it4i.cz

Karina Pešatová, IT4Innovations National Supercomputing Center

#### **IMPROVING RESPIRATORY VENTILATION WITH ADVANCED ICT ANALYTICS**

We expect an intensive care unit (ICU) to be the safest possible place, yet patients routinely receive mechanically assisted ventilation, which leads to the possibility of ventilator induced lung injury. Inflation of the alveoli generates stress forces which in turn create strain on the cells, which may lead to damage. The stress forces created by the inflation process are proportional to the tidal volume, a parameter that is defined on the mechanical ventilator, but needs to be optimized for gender and ideal body weight.

Queen's University Belfast, co-ordinator of the FP7 NanoStreams project, developed a system to monitor tidal volume and other airway pressure parameters associated with the respiratory physiology of patients. The system is known as VILIAlert and it is deployed in an ICU where patients are monitored continuously. The system is programmed to monitor various threshold violations (e.g. pressure in the patient's airways becoming too high or too low) and to report such events to the attending physicians in real time via SMS and other electronic media.

This builds upon previous NanoStreams work that calculated prices of financial options from a real-time streaming feed of stock prices. Here, the kernels were driven by for loops and alternatively by navigation of a binomial tree, yet monitoring of physiological parameters involves more logic and many more parameters. In addition, a fundamental component of our ventilator monitoring systems is a database,

HIPEACINFO 50 11

####

whereas, in the market data application, data relating to prices is processed straight off the wire.

For the financial use case, we defined new metrics of 'seconds per option' and 'joules per option' leading to a quality of service metric. One has no control over the arrival time of the next price update although, on a typical trading day, arrival intervals can be modelled using Poisson distribution. In contrast, human physiology is a continuous process measured by sensors that can be set to take recordings at predefined time intervals before forwarding them to a central database. Data is even routinely filtered at source so that only every third or fewer reading might be transmitted to the database. This is as much a function of the network infrastructure as of the scalability of the compute infrastructure.

# *"Monitoring of physiological parameters involves more logic and many more parameters."*

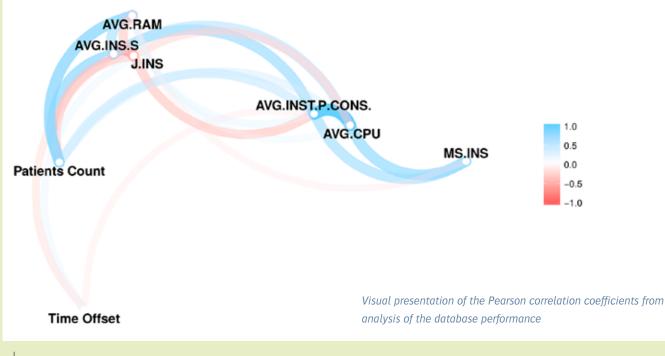

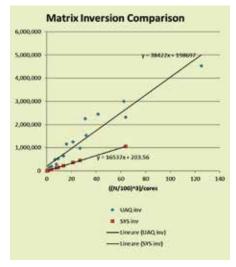

We extended the analysis in NanoStreams to derive metrics for the database component in our VILIAlert system and applied this to four open source databases (MySQL, PostgreSQL, ScaleDB and MariaDB), all of which have similar interfaces. In order to provide rigorous coverage of test cases, but within a reasonable amount of time, we used the statistical method of non-parameter bootstrapping. This reduced our run-time from 16 days to 36 hours. The image below presents the Pearson correlation coefficients for our analysis. Each metric is a node in the graph and the proximity of the metrics to each other represents the overall magnitude of their correlations. Thus clustering of the metrics is easily seen. Each path represents the correlation between the two variables. Blue and red paths represent positive and negative

correlations respectively, while the transparency and the width of the path represent the strength. Thinner and more transparent paths mean weaker correlation. We can see that Patients Count, average RAM used (AVG.RAM), average inserts per second (AVG.INS.S) and joules per insert (J.INS) form one cluster while AVG.INST.P.CONS (average instantaneous power), AVG.CPU (average CPU) and MS.INS (milliseconds per insert) form another distinct cluster. This means that increasing the number of patients has more impact on RAM usage than on CPU usage. This also means that databases that rely more on CPU than on RAM to handle an increased number of patients tend to have higher instantaneous power consumption than the databases that rely more on RAM. Apart from that, increased CPU usage implies an increment in the MS.INS metric. The best examples for this are ScaleDB and PostgreSQL, both of which had similar performance regarding the AVG.INS.S metric. ScaleDB handles an increased number of patients by using more CPU power and thus having the highest INST.P.CONS metric, while on the other hand PostgreSQL relies more on RAM and therefore has the lowest INST.P.CONS metric. Similarly, ScaleDB had the highest MS.INS metric, while the PostgreSQL had the lowest.

NanoStreams' overall mission is to explore domain-specific software stacks for real-time data analytics. In our work on physiological monitoring, where data ingress and storage is the dominant workload in comparison to SQL queries, we have identified distinct energy and performance characteristics for different databases. We have found that ScaleDB is an optimum database technology when handling between 200 and 800 patients in this application, while PostgreSQL performs best outside of this range.

Charles J Gillan, Murali Shyamsundar, Aleksandar Novakovic and Dimitrios S Nikolopoulos, Queen's University Belfast

#### WIDE-RANGING INNOVATIONS AT TU DELFT

Medicine and healthcare form one of the most notable achievements of all human endeavour, and resonate closely when our lives or those of our loved ones are affected by bad health. Traditionally, medicine has been a relatively conservative field in the way technology is used to support the activities of doctors or to facilitate new methods for diagnosis and treatment. However, as new technologies continue to prove their effectiveness and viability in clinical environments, more and more attention is being given to incorporating these technologies into common medical practices.

Our Computer Engineering Lab at the Delft University of Technology (NL) has taken notice of this trend, and has worked to establish a network of Dutch and European collaborators to investigate the potential impact of bringing the computer revolution to the medical world. The effort in our lab has two focal points: 1. investigating and enabling new technologies, and 2. facilitating and improving existing technologies.

#### **Enabling new technologies**

A good example is genetic research, which promises to become a game changer for the practice of medicine, by enabling personalized diagnostics and therapies to be developed for specific patient needs. Long and expensive compute times hinder the actual deployment of these techniques in patient care. Our lab has been collaborating with a number of institutes such as the German Cancer Research Center (DE) and Utrecht University Medical Center (NL) to accelerate their compute intensive algorithms, this enabling them to be used for patient diagnostics. Our lab has a high-tech startup called Bluebee that focuses on commercializing the genomics-related technologies that we develop.

Another standout example is research into the human brain, the socalled final frontier of science. This new and rather challenging field of research is expected to lead to a deep understanding of the root causes of mental illness and to help develop new effective therapies. The first step towards enabling this research involves simulating brain activity from the bottom up, by building brain models one cell at a time. Needless to say, such an activity is remarkably computationally intensive. Our lab is collaborating with partners such as the Erasmus Medical Center (NL) to accelerate and scale up these computations on high performance platforms, allowing the creation of bigger models that shed more insight into the functionality of the brain.

#### Improving existing technologies

Our lab is also working closely with a couple of organizations to improve the capabilities of existing medical procedures. One example is our collaboration with Leiden University Medical Center (NL) and Philips (NL) to manage the large size of medical imaging databases and to speed up image processing algorithms. This allows new modes of medical examination, where automated algorithms can support doctors to identify features in images or to combine and compare images for better or faster diagnosis. This also allows for new forms of intervention, such as minimally intrusive surgery, in which surgeons use imaging equipment and real-time processing to eliminate the need for direct visual inspection during surgery.

With our research, we aim to enable medical professionals to provide patients with better and more effective medical care, and give them a helping hand to integrate new technologies into this most valuable of human professions.

#### **AEGLE: HARNESSING BIG DATA TO FIND TOMORROW'S CURES**

Currently, healthcare applications only have access to a limited set of data, as data are usually fragmented, stored in different sites and with no easy access from external locations. In order to unlock the value of these data, a big data approach is needed. Analytics will help us understand the nature of various scientific questions and will allow us to integrate different data sources to help answer them. In addition, the adoption of a big data approach will enable the discovery of new correlations that are currently not foreseen, due to the fragmentation of datasets.

Focusing on healthcare, this approach could have an impact on the fields of medical imaging, oncology, intensive care units and healthcare policy making, as well as on the movement towards personalized management of chronic disease. This impact is twofold: on the one hand, it will enable healthcare stakeholders to develop cost-effective interventions, simultaneously improving patients' quality of life; while on the other, it will boost the activities of businesses developing big data health solutions.

Big data analytics are, in fact, becoming increasingly common in human-centred sciences, and ever-increasing data volumes have led to the development of new parallel processing models. However, data volumes are increasing at a faster pace than the available processing power, making it increasingly difficult to keep up with processing requirements.

#### The AEGLE solution: Big data for healthcare

An EU-funded Horizon2020 initiative implemented by 13 partners across Europe, AEGLE provides a framework for the management of big bioclinical data. The project addresses a number of challenges which can be divided into four main categories: user, technical, business and ethical, which reveal both the complexity of the project and the potential for impact on healthcare. AEGLE tackles performance and scalability challenges by building on heterogeneous acceleration, cloud and big data computing technologies to deliver optimized analytics services. Issues regarding the acceptance of the platform, problems regarding data integration, the nature of the AEGLE use cases, the sustainability of its business model and the management of legal and regulatory issues have already been identified, and their solutions are being incorporated into the system design.

Rather than just providing another multipurpose big data analytics platform, AEGLE incorporates health into the core of its activities. In

addition, to help overcome resistance to change, AEGLE is working on a regulatory framework needed for the adoption of new solutions, and has involved healthcare stakeholders in its activities from day one. Finally, AEGLE will provide a practical demonstration of the impact of big data on healthcare, by delivering three prototypes and by organizing awareness-raising activities to attract users and buyers. These activities are accompanied by a business model to enable the exploitation of results after the project ends.

Three use cases have been selected, covering a wide spectrum of healthcare:

- Type-2 diabetes, representing non-malignant chronic diseases. The AEGLE platform allows the interdependency of risk factors to be analysed so as to predict potential deterioration.

- Chronic lymphocytic leukaemia, an example of a malignant chronic disease. The AEGLE framework associates phenotypic data with personal genetic profiles and offers the possibility of identifying and evaluating treatment plans, with a view towards personalized medicine.

- Intensive care units, a typical paradigm of acute care. AEGLE aims to improve the management of clinical and laboratory data as well as physiologic waveforms. Its scalable data analytics will provide automated analysis of variables for the detection of unusual, unstable or deteriorating states in patients.

This approach will help AEGLE to include other cases within these categories, meaning the platform can be easily scaled up.

Overall, AEGLE aims to be the point of reference in big data applications for health that will create a multi-million euro business impact, enable thousands of researchers to exploit analytics and lead to increased acceptance of big data solutions in healthcare.

#### www.aegle-uhealth.eu

Andreas Raptopoulos, EXUS Innovation and Candela Bravo, LOBA

#### A TULIPP IN THE FIELD OF MEDICAL X-RAY IMAGING

Medical imaging is the visualization of body parts, organs, tissues or cells for clinical diagnosis and preoperative imaging. The global medical image processing market is about \$15 billion a year. The imaging techniques used in medical devices include a

variety of modern equipment in the fields of optical imaging, nuclear imaging, radiology and other image-guided intervention. The radiological method, or x-ray imaging, renders anatomical and physiological images of the human body at a very high spatial and temporal resolution.

Dedicated to x-ray instruments, the work of the Tulipp project is highly relevant to a significant part of the market share, in particular through its Mobile C-Arm use case, which is a perfect example of a medical system that improves surgical efficiency. In real time, during an operation, this device displays a view of the inside of a patient's body, allowing the surgeon to make small incisions rather than larger cuts and to target the region with greater accuracy. This leads to faster recovery times and lower risks of hospital-acquired infection. The drawback of this is the radiation dose: 30 times what we receive from our natural surroundings each day. This radiation is received not only by the patient but also by the medical staff, week in, week out.

While the x-ray sensor is very sensitive, lowering the emission dose increases the level of noise on the pictures, making it unreadable. This can be corrected with proper processing.

From a regulatory point of view, the radiation that the patient is exposed to must have a specific purpose. Thus, each photon that passes through the patient and is received by the sensor must be delivered to the practitioner; no frame should ever be lost. This brings about the need to manage side by side strong real-time constraints and high-performance computing.

We managed to lower the radiation dose by 75% and restore the original quality of the picture thanks to specific noise reduction algorithms running on high-end PCs. However, this is unfortunately not convenient when size and mobility matter, like in a confined environment such as an operating theatre, crowded with staff and equipment. Yet by providing the computing power of a PC in a device the size of a smartphone, Tulipp makes it possible to lower the radiation dose while maintaining the picture quality. To achieve this, a holistic view of the system is required so as to achieve the best power efficiency from inevitably highly heterogeneous hardware.

With our power-aware tool chain, the application designer can see, for each mapping of the application tasks on the hardware resources, the impact on power consumption. He or she can thus schedule the processing chain to optimize both the performance and the required energy. The tool chain relies on a low-power real-time operating system. Specifically designed to fit in the small memory sizes of embedded devices, it comes with an optimized implementation of a necessary set of common image processing libraries and allows seamless scheduling of the application on the hardware chips.

Philippe Millet, Thales

A Tulipp Hardware Instance

This issue's round-up of news and results from EU-funded projects includes the final outcomes of major projects ASPIRE, EUROSERVER, ASAP and HARPA, as well as giving an update on work on aircraft design in the MIKELANGELO consortium.

# **Innovation Europe**

#### COST-EFFICIENT WAYS TO MANAGE PERFORMANCE VARIABILITY

HARTA Continuously increasing application demands on both high-performance computing (HPC) and embedded systems (ES) are driving the

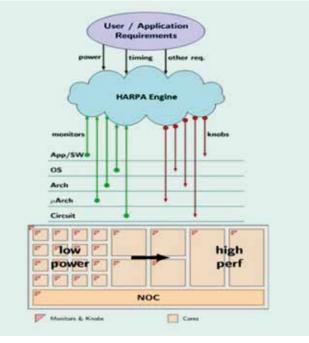

information and communications manufacturing industry to a never-ending scaling of silicon devices. Nevertheless, integration and miniaturization of transistors comes with an important and non-negligible trade-off: time-zero and time-dependent performance variability. The HARPA project, which ended in late 2016, aimed to enable next-generation embedded and high-performance heterogeneous many-cores to cost-effectively confront variations by providing 'dependable performance': correct functionality and timing guarantees throughout the expected lifetime of a platform within thermal, power and energy constraints. The HARPA novelty is in seeking synergies in techniques that have been considered virtually exclusively in the ES or HPC domains (worst-case guaranteed partly proactive techniques in embedded, and dynamic best-effort reactive techniques in high-performance).

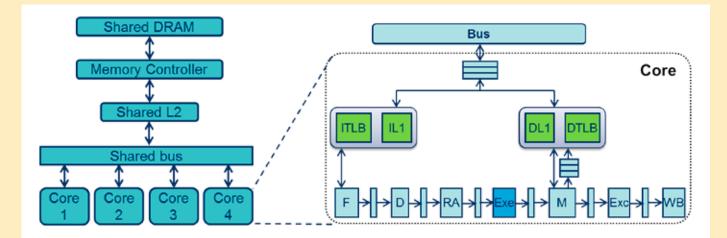

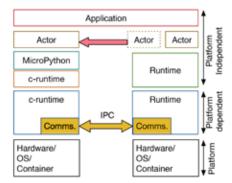

The industry and academic partners of the pan-European HARPA team specialized in fields covering all abstraction layers, from hardware to application level. The project developed a set of monitors/knobs in hardware and software designs that observes performance unpredictability, triggering system reactions. The figure below provides an overview of the HARPA engine.

It is a middleware split between the Operating System (HARPA-OS) and the hardware actuators (HARPA-RTE) and provides run-time

dependable performance guarantees. HARPA-OS applies resource allocation policies, arbitrating the OS calls with a by-second time granularity. HARPA-RT sits at a low level in the system stack, achieving a millisecond control on hardware resources. HARPA-OS and HARPA-RTE cooperate to ensure the performance dependability goals, keeping a prompt low-level control on hardware resources. Run-time reactive and proactive techniques have been deployed, ensuring that the combined monitor/ scheduling/knob reaction latency never violates the application deadlines. These techniques were tested on industrial applications running on embedded platforms and a full-system evaluation framework simulating HPC setups. A fundamental objective of the project was to provide solutions to mitigate reliability threats and ensure dependable system performance. To this end, the HARPA engine was developed, implementing various control frameworks across the system stack. The goal was to exploit different manifestations of platform slack (i.e. slack in performance, power, energy, temperature, lifetime or structures/components), in order to ascertain timing guarantees throughout the lifetime of the device. A component of the HARPA engine is the HARPA-OS, the system-wide resource manager developed by POLIMI. This component must include control policies capable of providing a response in a timeframe spanning from hundreds of milliseconds to a second. The HARPA-RTE sits at a low level in the system stack and is in direct contact with the various monitors and knobs. It has responsive control on hardware resources, enabling extremely fast adaptation to system behaviour in the scale of some milliseconds, which is ideal for providing guarantees for hard-deadline applications and complements the comparatively slower responsiveness of the HARPA-OS.

The concepts developed within the HARPA context addressed both the HPC and ES domains equally. Specifically, from the HPC domain we used disaster and flood management simulation, while, from the ES domain, a radio frequency spectrum sensing application, a face detection application, object recognition and the Beesper Landslide Multimodal Monitoring. In particular, HARPA use cases demonstrated in HPC platforms: (i) Intel Xeon, (ii) x86-64 multi-core plus a GPU and embedded platforms: (a) Freescale i.MX 6Quad, (b) ODROID XU-3 (Octa Core Linux Computer Samsung Exynos5422 Cortex-A15 2.0Ghz quad core and Cortex-A7 quad core).

WEBSITE: www.harpa-project.eu

The HARPA project received funding from the European Union's FP7 Programme under grant agreement no. 612069.

#### THE MIKELANGELO APPROACH TO HPC SIMULATIONS AND AIRCRAFT DESIGN

When high performance of a computer infrastructure is needed, we usually choose to use HPC. However, when flexibility and adaptability are required, we tend to opt for

the HPC cloud. In such cases, we amalgamate the best of both worlds: the performance of HPC and the flexibility of the cloud. However, the combination of these approaches presents us with challenges. When performance, flexibility and security of the virtualized infrastructure are required, software adaptations are necessary alongside the use of HPC. Enter MIKELANGELO, a Horizon 2020-funded HPC cloud research project. MIKELANGELO is boosting performance of VMs (Virtual Machines utilizing the hardware structure of a physical host) and I/O (input/output) operations by deploying their innovative technologies: I/O boosting updates to KVM (Kernel-based Virtual Machine), OSv unikernel for fast and secure workloads, OpenStack and Torque compatibility and deployment-ready OpenFOAM HPC cloud components.

Able to boot in less than a second, OSv (an open source operating system designed for the cloud) can execute applications on top of any hypervisor, resulting in superior performance, speed and effortless management. Many applications, including HPC and the big data business cases steering the MIKELANGELO project, directly benefit from those features.

Efficiency and speed of input/output operations is especially important in the light aircraft design process, running heavily parallelized numerical simulations to improve aerodynamic properties at an early stage. The Slovenian aircraft manufacturer Pipistrel uses computational fluid dynamics (CFD) simulations on a computer to simulate the flow of air around an aircraft and analyse aerodynamic features of their designs without timeconsuming and expensive manufacturing.

OpenFOAM, the most widely used general-purpose open source software package for CFD is ideal when it comes to designing new aeroplanes or even just improving parts of existing aeroplanes. Pipistrel currently runs many consecutive cases either on a local machine or on a remote cluster. In either case, the target machines need to be specifically configured to run OpenFOAM requests.

The OpenFOAM cloud, developed within MIKELANGELO, along with highly optimized I/O components built directly into KVM can be deployed on top of any hardware (cluster, HPC hardware, cloud hardware). Its functionalities, flexibility, modality and ease

NAME: Harnessing Performance Variability (HARPA) START/END DATE: 01/09/2013 – 30/11/2016

KEYWORDS: many-core, high-performance architectures, thermal related reliability, dependability, adaptive systems, energy efficiency, performance and timing analysis, run-time resource management PARTNERS: Politecnico di Milano (Italy), Interuniversitair Micro-Electronicacentrum Imec (Belgium), University of Cyprus (Cyprus), Vysoka Skola Banska - Technicka Univerzita Ostrava (Czech Republic), Thales Communications & Security (France), Institute of Communication and Computer Systems (Greece), HENESIS (Italy) BUDGET: €3.9M

#### **Innovation Europe**

of deployment are exposed through a lightweight OpenStack dashboard allowing users to focus on the simulation design rather than on cluster deployment, management and support.

The HPC cloud approach developed through MIKELANGELO brings together the best of both worlds: the raw performance of HPC infrastructure and the flexibility of clouds. The MIKELANGELO team are working tirelessly to maximize achievements in both of these areas of strength, using unikernels and optimized virtualization infrastructure (IO efficient KVM) to reduce the virtualization impact on one hand, and optimizing the actual software packages (e.g. openFOAM) to perform on such infrastructure on the other.

MIKELANGELO meeting – Pipistrel's headquarters, Ajdovščina, Slovenia

NAME: MIKELANGELO - MIcro KErneL virtualizAtioN for hiGh pErfOrmance cLOud and hpc systems

START/END DATE: 01/01/2015 - 31/12/2017

KEYWORDS: HPC, cloud, simulations, aircraft design, unikernels, OpenFOAM

PARTNERS: XLAB (Slovenia – coordinator), Huawei Technologies Düsseldorf (Germany), IBM Israel, Intel Research & Development Ireland, ScyllaDB (Israel), Universitaet Stuttgart (Germany), GWDG (Germany), Ben-Gurion University of the Negev (Israel), Pipistrel (Slovenia)

#### BUDGET: €5.99M

WEBSITE: www.mikelangelo-project.eu

MIKELANGELO is funded by the European Commission's Horizon 2020 Framework Programme under grant agreement no. 645402.

#### FLEXIBLE & SCALABLE DATA ANALYTICS

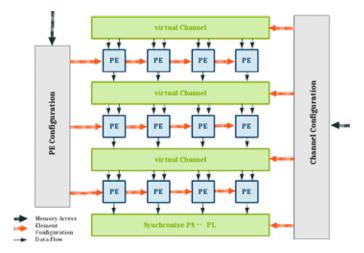

Recently concluded, the ASAP FP7 project has developed a dynamic open-source execution framework for scalable data analytics. The driving idea was that no

single execution model is suitable for all types of tasks, and no single data model (and store) is suitable for all types of data. Complex analytical tasks over multi-engine environments therefore require integrated profiling, modelling, planning and scheduling functions.

The ASAP project pursued four main goals:

- 1.A modelling framework that constantly evaluates the cost, quality and performance of available computational resources in order to decide on the most advantageous store, indexing and execution pattern.

- 2. A generic programming model in conjunction with a runtime system for execution in the cloud. The execution can target clusters using an extended and augmented version of Spark, or multiprocessors using the high-performance Swan task-parallel execution engine. State-of-the-art features include: irregular general-purpose computations, resource elasticity, synchronization, data transfer, locality and scheduling abstraction, ability to handle large sets of irregularly distributed data, and fault tolerance. To overcome Spark's limitations on irregular loads, the project has augmented the Spark runtime with full support for general-purpose, recursive computations.

- 3.A unique adaptation methodology that enables analytics experts to amend submitted tasks in later processing stages. In combination with visualization and monitoring of workflows, this enables data scientists and analytics engineers to fine-tune workflows and speed up development time as well as understand and adjust performance in production.

- 4. A real-time visualization engine to show the results of the initiated tasks and queries in an intuitive manner -- building on the dashboard of the Media Watch on Climate Change and the faceted search developed for the Climate Resilience Toolkit.

The ASAP consortium brought together partner expertise in data analytics, runtime systems, scheduling and cost estimation, programming models, optimization, data science and visualization. Towards the latter stages of the project, the consortium focused on integrating all of the ASAP modules into a single open-source framework. The ASAP platform is open and available for download and use, and incorporates research results that have advanced the state of the art in multiple fields and resulted in tens of publications.

The platform has already been deployed in production, on two industrial applications within the project, to manage complex workflows on web content analytics and telecommunication data analytics:

- The Web Content Analytics use case is centred on the services of Internet Memory Research. These services provide access to a very large collection of content extracted from the web, cleaned, annotated and indexed in a distributed infrastructure. Previously, this was mainly based on Hadoop components. ASAP extended the workflow interface used by IMR to make workflow editing easier and automatically produce optimal workflow materializations, by learning the performance of each component and automatically selecting optimal workflow components from all available implementations.

- The **Telecommunication Data Analytics** use case mines call data record data by WIND Telecomunicazioni, for user classification, prediction of network load and detection of unusual events from mobile phone calling patterns. The telecommunication data is combined with data mined from social media and visualized to help analysts gain better insights, detect special events that influence network traffic, and make overall better predictions and decisions. Technology developed within ASAP helped WIND engineers develop these applications, manage their execution, and scaled their analysis to many millions of mobile phone calls in a greatly reduced amount of time.

NAME: A Scalable Analytics Platform (ASAP)

START/END DATE: 01/03/2014 - 28/02/2017

**KEYWORDS:** big data analytics, heterogeneous platforms, workflow design, workflow scheduling

PARTNERS: Foundation for Research and Technology – Hellas (Greece), Université de Genève (Switzerland), Institute of Communication and Computer Systems (Greece), Queen's University Belfast (UK), Internet Memory Research (France), WIND Telecomunicazioni (Italy), webLyzard technology (Austria)

BUDGET: €3.6M

WEBSITE: www.asap-fp7.eu

The ASAP project received funding from the European Union's FP7 Programme under grant agreement no. 619706.

#### MAKING MOBILE DEVICES MORE SECURE WITH THE ASPIRE FRAMEWORK

#### In January 2017, the ASPIRE project was evaluated as 'excellent' at its final project review with the European Commission.

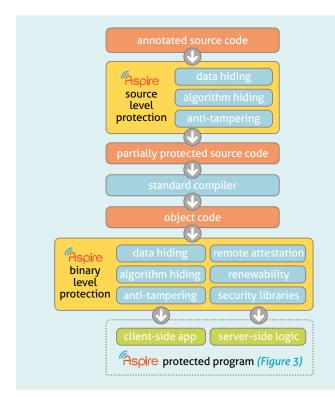

The mission of ASPIRE was to integrate state-of-the-art software protections into an application reference architecture and into an easy-to-use compiler framework that automatically provides measurable software-based protection of the valuable assets in the persistently or occasionally connected client applications of mobile service, software and content providers.

For mobile devices like smartphones and tablets, security solutions based on custom hardware (as is traditionally done with smart cards, set-top boxes and dongles, for example) are not convenient. Software protection is therefore of utmost importance; it can be a maker or a breaker of a product or service, or even a business. Current software protection techniques are incredibly hard to deploy, cost too much and limit innovation. Stakeholders in mobile devices need more trustworthy, cheaper software security solutions and more value for the money they spend on software security. In this project, three market leaders in security ICT solutions and four academic institutions joined forces to protect the assets of one class of stakeholders: the service, software, and content providers. From their perspective, mobile devices and their users, which can engage in attacks on the software and credentials installed to access the services or content, are not trustworthy.

# Final results and their potential impact and use

The software protection technology that has been developed consists of:

- (i) the ASPIRE reference architecture for combining and composing multiple layers and types of software protections;

- (ii) designs and implementations of a range of online and offline protections, some of which pre-existed, some which are new or significant improvements over the previous state of the art;

- (iii) the robust ASPIRE Compiler Tool Chain that enables the automated, combined deployment of combinations of protections on real-world use cases;

- (iv) the ASPIRE Decision Support System and its ASPIRE Knowledge Base to assist the user of the tool chain with the selection of the protections best suited to protect the software and the assets embedded in it; and

- (v) the ASPIRE software protection evaluation methodology to assess the value of software protections vis-à-vis man at the end attacks.

#### **Innovation Europe**

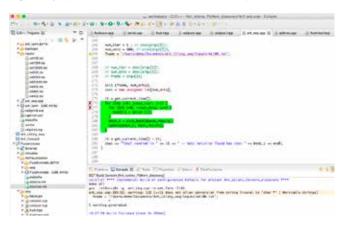

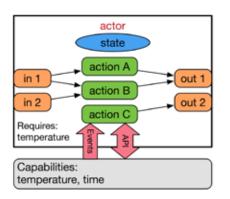

The ASPIRE Compiler Tool Chain is based on plug-ins. Its overall flow is shown in the figure above. First, a sequence of source-tosource rewriting plug-ins are invoked. Each of them takes as input (pre-processed) C code and produces the same format. This facilitates the insertion of additional plug-ins. All the plug-in transformations are controlled by pragmas and attributes with which the assets to be protected have been annotated. Concrete annotations are available to specify concrete protections. Abstract requirement protections are supported as well, with which the developer can specify the security requirements on the assets (integrity, confidentiality, and so on). The ASPIRE Decision Support system then converts those requirements into specifications of protections to be deployed. The final source-level plug-in extracts the remaining annotations from the source code, which is then compiled with GCC or LLVM into standard object code, and linked with binutils (binary utilities). Plug-ins in the link-time binary code rewriting framework Diablo then apply further transformations to deploy additional protections and to finalize some of the protections of which the first analysis and transformation steps were initiated on the source code.

The prototype implementation available on GitHub supports the protection of Linux and Android ARMv7 binaries and dynamically linked libraries compiled from C and C++ code. Only the C code is protected, however. The tools have been extensively tested and validated on native Android libraries that are packed in Android packages (together with Java apps) and in plug-ins that provide vendor-specific crypto and DRM services in the Android DRM and mediaserver framework.

A large part of the developed software prototypes is available as open source with extensive documentation, and more than 30 demonstration videos have been published on the project's demonstration Youtube channel. A significant part of the research has already been peer reviewed and many additional papers are still in the pipeline. Through keynotes and tutorials, including in workshops organized by the consortium, the European software protection community has been revitalized and has been made well aware of the project and its results.

#### **Exploitation and impact**

Some of the project results are already ready for commercial exploitation. A spin-off is in the making at Fondazione Bruno Kessler, and a technology transfer from the University of Ghent to industry has already taken place. Some of the specific protections developed within the project are used in products in the pipeline in business units of the industrial partners. As such, the project strengthens the position of European companies, including, of course, the project partners, whose business models depend on securing the assets embedded in their software. Other results are not ready for immediate commercialization. But with the whole ASPIRE Framework encompassing the compiler tool chain, the decision support system, many protections, and tools that automate the application of the software protection evaluation methodology, the consortium has demonstrated that measureable, assisted deployment of software protection is feasible. The open source availability of the framework will help the European R&D community to bridge the gap to commercial deployment of the ASPIRE approach, not least by providing all the foundational infrastructure necessary for complementing and expanding the expert knowledge already amassed in the project from the researchers' expertise, from professional penetration tests, from a public challenge, and from external advice.

YouTube demo video channel: https://www.youtube.com/channel/ UCntMGBjHr\_oW5wEd5JgjD6g

Open source repository: https://github.com/aspire-fp7

NAME: Advanced Software Protection: Integration, Research and Exploitation (ASPIRE)

KEYWORDS: mobile software security, compiler, decision support, evaluation methodology

PARTNERS: Universiteit Gent (Belgium), Nagravision (Switzerland), SFNT Germany, Gemalto (France), Fondazione Bruno Kessler (Italy), Politecnico di Torino (Italy), University of East London (UK) BUDGET: €4.6M

WEBSITE: www.aspire-fp7.eu

START/END DATE: 01/11/2013 - 31/10/2016

The ASPIRE project received funding from the European Union's FP7 Programme under grant agreement no. 609734.

#### **LEADING DATA CENTRES INTO** THE FUTURE: EUROSERVER

Tasked with developing an energy-efficient server design that could be used to meet SERVER the demands expected for exascale

computing beyond 2020, the EUROSERVER team has concluded the project having produced solutions which could halve the cost of powering data centres and well as greatly increase performance through memory compression.

The project has also led to the development of two spin-off companies; KALEAO Ltd., headquartered in Cambridge, UK and ZeroPoint Technologies, a startup that has come out of Chalmers University of Technology in Gothenburg.

But what were the stages that took place behind these impressive outcomes and what new technical knowledge has been gained?

#### **Getting ARM-based microserver designs** into the data centre

Consortium partner ARM is a dominant force in the mobile device market where the energy-efficiency and popular instruction set of its processors has led to it being the instruction set of choice for mobile developers. Over the last few years, ARMdesigned processors have looked to challenge the Intel-dominated data centre market.

The table below shows the experimental platforms that were investigated. They include a Juno ARM 64-bit development platform, a Trenz board with four energy-efficient Cortex-A53 ARM 64-bit processors and an Intel Xeon D-1540 that we believe is a realistic competitor to ARM in the energy-efficient compute domain.

|                                        | Juno r2<br>Development Platform              | Trenz<br>Development<br>Platform | Intel Xeon D-1540                   |  |

|----------------------------------------|----------------------------------------------|----------------------------------|-------------------------------------|--|

| Cores                                  | 2x Cortex-A72<br>4x Cortex-A53               | 4x Cortex A53                    | 8x Broadwell cores<br>16 hw threads |  |

| Clock Speed                            | Cortex-A72 @ 1.2 GHz<br>Cortex-A53 @ 950 MHz | 1.2 GHz                          | 2 GHz                               |  |

| L1 Data<br>Cache                       | 48 kB per core                               | 32 kB per core                   | 32 kB per core                      |  |

| L1 Instruction<br>Cache 32 kB per core |                                              | 32 k8 per core                   | 32 k8 per core                      |  |

| L2 Cache                               | 2 MB shared                                  | 1 MB shared                      | 256 kB per core                     |  |

| L3 Coche                               |                                              | 2                                | 12 MB                               |  |

| RAM                                    | 8 GB<br>DDR3L Dual Channel                   | 4 GB<br>DDR3L Dual Channel       | 32 GB<br>DDR4 Dual Channel          |  |

The EUROSERVER platforms that were analysed

Some early adopters tried to integrate ARM processors into the data centre but used the ARM 32-bit architecture and hence the idea didn't gain traction. This has all changed with the advent of the 64-bit ARM architecture and, since then, many companies have investigated placing ARM-based micro-server designs into the data centre.

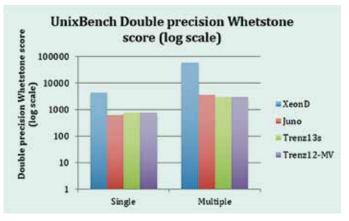

Yet ARM-based processors need to catch up with the large leadtime and massive inertia that Intel has established, the latter having control over the entire ecosystem from design through to fabrication. Intel-based processors make up 98% of the data centre market. The scores of typical benchmarks, such as UnixBench, suggest that Intel solutions are at least one order of magnitude more capable than the ARM-based solutions that are trying to compete with them, as shown in figure 1 below. Where EUROSERVER came in was to develop a server design that benefited from ARM's power efficiency and addresses some of its shortcomings so as to create a viable alternative to Intel-based solutions.

1: UnixBench, Whetstone test results for various devices under test (log scale)

#### "EUROSERVER's solutions could halve the cost of powering data centres and greatly increase performance"

#### Hardware advances

Over the course of the project, a combination of hardware and software techniques were developed. On the hardware side, two prototype platform testbeds were created: a Juno R2 development board based system and a Trenz development platform. Both have energy-efficient, quad-core ARM 64-bit Cortex A53 processors, with the Juno differing in that it is also a big.LITTLE design and has a Cortex-A72.

The Trenz 0808-based, UltraScale+ system, seen in figure 2, combines a Trenz module with 4x A53 cores with a placeholder for a System-In-Package (SIP) 32-core A53. At the time of writing, the 32-core SIP is not ready but will be included in one of the

#### **Innovation Europe**

follow-up projects that has resulted from EUROSERVER, including ExaNeSt, ExaNoDe and EcoScale.

2: The EUROSERVER designed, NEAT produced, prototype board. Not shown are a Trenz 0808 module and a SIP

#### Software breakthroughs

Processor manufacturers in recent years have been limited in how far the frequency envelope can be pushed due to power density, which has led to the rise of multicore chips. EUROSERVER has taken on board this change in design and has developed new scalable technologies, UNIMEM and the MicroVisor, that allow better scaling of compute and memory resources. These will be able to deal better with the exascale computing workloads that are expected in future data centres.

UNIMEM is a shared memory technology that allows multiple boards to share memory regions between them. This allows for better provisioning strategies and for greater in-memory workloads than are possible with current best-of-breed solutions. Memory from each board is divided into a local and a remotely addressable region. UNIMEM technology is a licensed IP technology and has been investigated by a number of companies and research organizations.

The MicroVisor is a new hypervisor technology derived from Xen. It is purpose made for low-power, energy-efficient platforms such as ARM that have many, albeit weaker cores. Traditional hypervisors are now quite 'bloated' and require a large amount of resources that are not available to ARM-based boards. Instead a lighter, more efficient platform has been developed that works natively with ARM and Intel architectures. The overhead for workloads running in virtual machines is near negligible, as seen in figure 1.

"ARM-based designs will have a place in the data centre of the future

#### **Energy-efficient platforms**

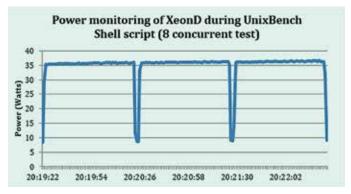

Power monitoring techniques such as RAPL are used to expose the power utilized by the XeonD platform to be able to identify the power used by the processor during stages of a workload (see figure 3).

3: Power monitoring of the Intel XeonD while running a UnixBench Shell script test

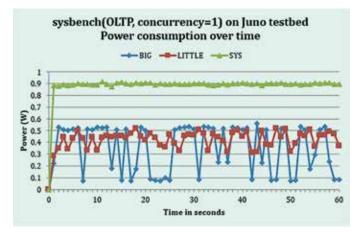

The equivalent power monitoring has been exposed through kernel modules in the Juno platform to allow monitoring of the ARM system whilst running workloads (see figure 4).

4: Power monitoring of the Juno R1 development board, whilst running SysBench OLTP workload

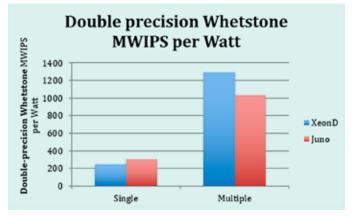

By looking at the power profile of the devices while investigating the workloads it is then possible to identify the power-efficiency of the platforms - as seen in figures 5 and 6. The power efficiency of the Juno platform shows that, although the ARM-based designs lag behind in raw performance values, they are more energyefficient and will have a place in the data centre of the future.

5: These energy efficiencies were calculated by taking the Whetstone score and dividing by the average power usage recorded for the processor during this test

The final EUROSERVER platform (see figure 7) combines a pair of UltraScale+ boards on a backplane that provides electrical and physical connectivity. These boards will be used in the several follow-up projects to form the basis of a 'European server', a server designed and built in the EU that will keep the continent competitive in the ever-changing global ICT market .

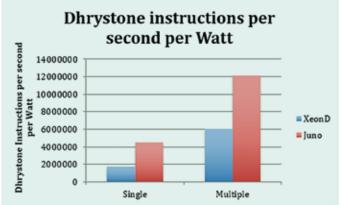

6: These energy efficiency values were calculated by taking the Dhrystone scores and then dividing by the average power usage during this test

NAME: EUROSERVER: Green computing node for European micro-servers

START/END DATE: 01/09/2013 - 31/01/2017

KEYWORDS: microserver, energy-efficiency, memory compression,

hypervisor, system integration, true convergence

PARTNERS: CEA-Leti (France), OnApp (UK), Foundation for Research and

Technology Hellas (Greece), Barcelona Supercomputing Center (Spain),

TU Delft (Netherlands), STMicroelectronics (France), NEAT (Italy),

Chalmers University of Technology (Sweden) and ARM (UK)

BUDGET: €11.4M

WEBSITE: www.euroserver-project.eu

The EUROSERVER project received funding from the European Union's FP7 Programme under grant agreement no. 610456.

7: A pair of EUROSERVER boards, assembled onto a backplane with electrical connectivity, designed by EUROSERVER and produced by NEAT

# 2016 HiPEAC Technology Transfer Awards